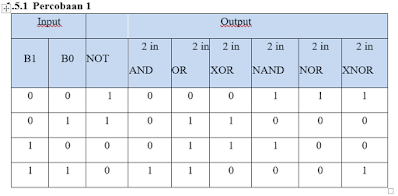

Laporan Akhir 1 (Percobaan 1)

|

Input |

|

|

B1 |

B0 |

|

0 |

0 |

|

0 |

1 |

|

1 |

0 |

|

1 |

1 |

Data yang didapatkan dibandingkan dengan teori

adalah sebagai:

Ø

Not (Inverter)

|

Input |

Output

Praktikum |

Output Teori |

|

0 |

1 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

|

1 |

0 |

0 |

Dari tabel tersebut

dapat disimpulkan bahwa dengan input yang sama output yang didapatkan dari

simulasi rangkaian dan output dari tabel kebenaran adalah sama. Apabila input

adalah logika ‘0’ maka akan dihasilkan output logika ‘1’. Sebaliknya, apabila

input berlogika ‘1’ maka akan dihasilkan output berlogika ‘0’. Atau output

adalah kebalikan dari input inverter tersebut.

Ø

AND

|

Input |

Output |

||

|

B1 |

B0 |

Praktikum |

Teori |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

Dari tabel tersebut

dapat disimpulkan bahwa dengan input yang sama output yang didapatkan dari

simulasi rangkaian dan output dari tabel kebenaran adalah sama. Apabila salah

satu input berlogika ‘0’ maka akan dihasilkan output logika ‘0’. Sedangkan

apabila kedua input berlogika ‘1’ maka akan dihasilkan output berlogika ‘1’.

Ø

OR

|

Input |

Output |

||

|

B1 |

B0 |

Praktikum |

Teori |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

1 |

Dari tabel tersebut

dapat disimpulkan bahwa dengan input yang sama output yang didapatkan dari

simulasi rangkaian dan output dari tabel kebenaran adalah sama. Apabila salah

satu input berlogika ‘1’ maka akan dihasilkan output logika ‘1’. Sedangkan

apabila kedua input berlogika ‘0’ maka akan dihasilkan output berlogika ‘1’.

Ø

XOR

|

Input |

Output |

||

|

B1 |

B0 |

Praktikum |

Teori |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

Dari tabel tersebut

dapat disimpulkan bahwa dengan input yang sama output yang didapatkan dari

simulasi rangkaian dan output dari tabel kebenaran adalah sama. Apabila kedua

input berlogika sama maka akan dihasilkan output logika ‘0’. Sedangkan

apabila kedua input memiliki logika yang berbeda maka akan dihasilkan output

berlogika ‘1’.

Ø

NAND

|

Input |

Output |

||

|

B1 |

B0 |

Praktikum |

Teori |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

Dari tabel tersebut dapat

disimpulkan bahwa dengan input yang sama output yang didapatkan dari simulasi

rangkaian dan output dari tabel kebenaran adalah sama. Apabila salah satu input

berlogika ‘0’ maka akan dihasilkan output logika ‘1’. Sedangkan apabila kedua

input berlogika ‘1’ maka akan dihasilkan output berlogika ‘0’.

Ø

NOR

|

Input |

Output |

||

|

B1 |

B0 |

Praktikum |

Teori |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

Dari tabel tersebut

dapat disimpulkan bahwa dengan input yang sama output yang didapatkan dari

simulasi rangkaian dan output dari tabel kebenaran adalah sama. Output yang

dihasilkan adalah kebalikan dari gerbang OR. Apabila salah satu input berlogika

‘0’ maka akan dihasilkan output logika ‘0’. Sedangkan apabila kedua input

berlogika ‘0’ maka akan dihasilkan output berlogika ‘1’.

Ø

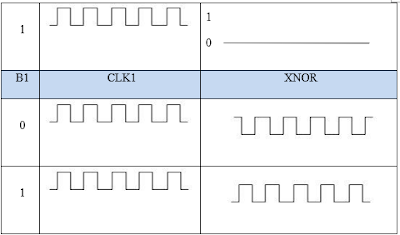

XNOR

|

Input |

Output |

||

|

B1 |

B0 |

Praktikum |

Teori |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

Dari tabel tersebut

dapat disimpulkan bahwa dengan input yang sama output yang didapatkan dari

simulasi rangkaian dan output dari tabel kebenaran adalah sama. Apabila kedua

input memiliki logika yang sama maka akan dihasilkan output logika ‘1’.

Sedangkan apabila kedua input memiliki logika yang berbeda maka akan dihasilkan

output berlogika ‘0’.

Tidak ada komentar:

Posting Komentar